The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

# TM 990/305 COMBINATION MEMORY AND I/O EXPANSION MODULE

**APRIL 1979**

TEXAS INSTRUMENTS

the state

# IMPORTANT NOTICES

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best possible product.

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

No part of this document may be copied or reproduced in any form without the prior written consent of Texas Instruments Incorporated.

Copyright © 1979

TEXAS INSTRUMENTS INCORPORATED

# TABLE OF CONTENTS

| SEC | TION                                                                                      | TITLE Jugal Pass                                                                                                                                                                                           |         | PAGE                                                                                    |

|-----|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------|

| 1.  | INTRODUCT                                                                                 |                                                                                                                                                                                                            |         |                                                                                         |

|     | 1.2 Manu<br>1.3 Modu<br>1.4 Gene                                                          | eral ual Organization ule Characteristics eral Specifications licable Documents                                                                                                                            |         | 1-2<br>1-2<br>1-2                                                                       |

| 2.  | 2.1 Gene<br>2.2 Requ<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2. | 2 Terminal Device 3 Power Supply 4 Card Cage/System Bus Connector 5 Parallel I/O Connector acking And Inspection per Configuration As Shipped tch Configuration As Shipped er Supply Connections tallation |         | 2-1<br>2-1<br>2-1<br>2-1<br>2-2<br>2-2<br>2-2<br>2-3<br>2-3<br>2-3<br>2-4<br>2-5<br>2-6 |

| 3.  | 3.1 Gene<br>3.2 Memo<br>3.3 Memo<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3                | .2 Memory Page Select                                                                                                                                                                                      |         | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>3-5<br>3-5                                           |

| 4.  | 4.1 Gen<br>4.2 POR<br>4.3 POR<br>4.3<br>4.3                                               | TPUT PORT CONFIGURATION eral T 0 T 11 Input/Interrupt Enable2 Interrupt Select3 Interrupt Configuration                                                                                                    |         | 4-1<br>4-1<br>4-3<br>4-3                                                                |

| 5.  | 5.1 Gene<br>5.2 I/O<br>5.3 CRU<br>5.4 Sel                                                 | INTERRUPT PROGRAMMING eral  Ports At Edge Connectors P2 And P3  Base Address Nomenclature ecting Most Significant Bits Of CRU Hardware Base siderations.                                                   | Address | 5-1<br>5-2<br>5-3                                                                       |

| SWIND THANKS | 5.6   | 5.5.1 Configure Port 0 For Either Input Or Output. 5.5.2 Enable Output Bit. 5.5.3 Disable Output Bit. 5.5.4 Read Input Bit. Programing Examples. 5.6.1 Write A One To Port 0 Output Bit 0. 5.6.2 Input A Bit From Port 0 Input Bit 0. 5.6.3 Write All Ones To Port 0 Output Bits 0-6. 5.6.4 Write All Ones To Port 0 Output Bits 0-9, Read Values At Port 0 Input Bits 10-15. 5.6.5 Read Port 1 Input Bits 0-15. 5.6.6 Test Port 1 Input Bits 7, Wait Until Enabled. 5.6.7 Interrupts. 5.6.7.1 Enable INTO, Wait For Interrupt. 5.6.7.2 Enable INTO, INT1 Masks; Disable INT2, INT3 Masks. 5.6.7.3 Reset All Interrupts And Masks. 5.6.7.5 Board Interrupt Check, Poll If Enabled. 5.6.8 Reset Board. 5.6.9 LEDs DS1 And DS2. 5.6.9.1 Turn On And Off LEDs DS1 And DS2. 5.6.9.2 Blink LEDs. | 5-7<br>5-8<br>5-8<br>5-9<br>5-9<br>5-10<br>5-10<br>5-12<br>5-12<br>5-12<br>5-12<br>5-13<br>5-13 |

|--------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 6.           | THEOR | 5.6.9.2 Blink LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |

|              | 6.2   | System Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-1                                                                                             |

|              |       | 6.3.1 Address Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                 |

|              |       | 6.3.3 CRU Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                 |

|              | 6.4   | Quick Reference Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-5                                                                                             |

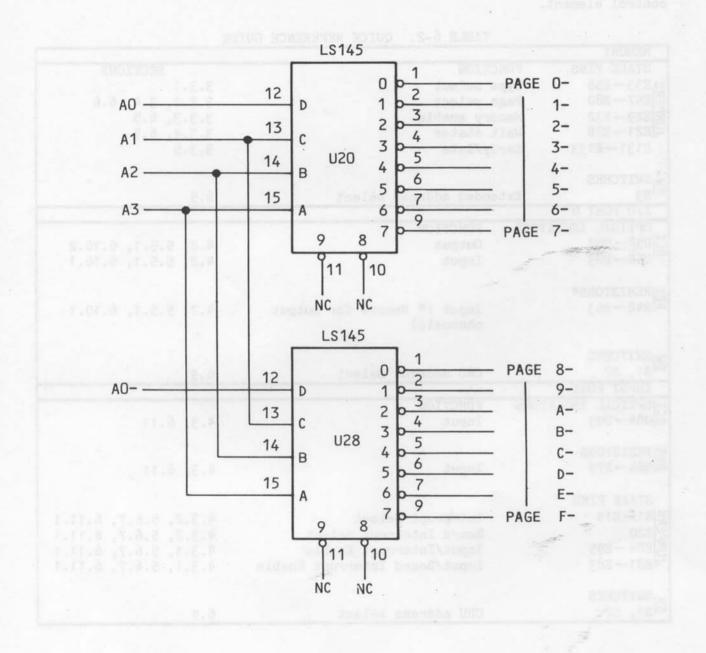

|              | 6.6   | Memory Address Decoding  Memory Page Selection  6.6.1 Page Select Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-8                                                                                             |

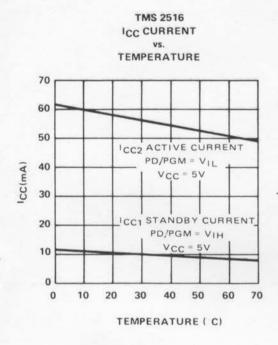

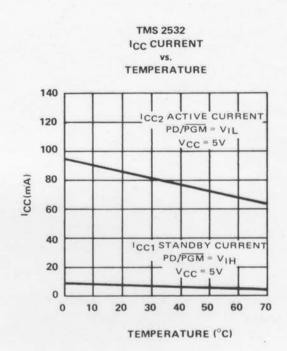

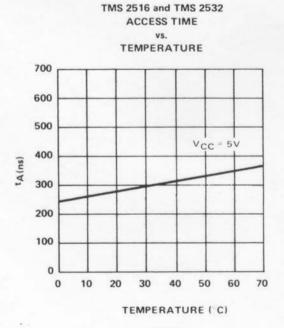

|              | 6.7   | Memory Access Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |

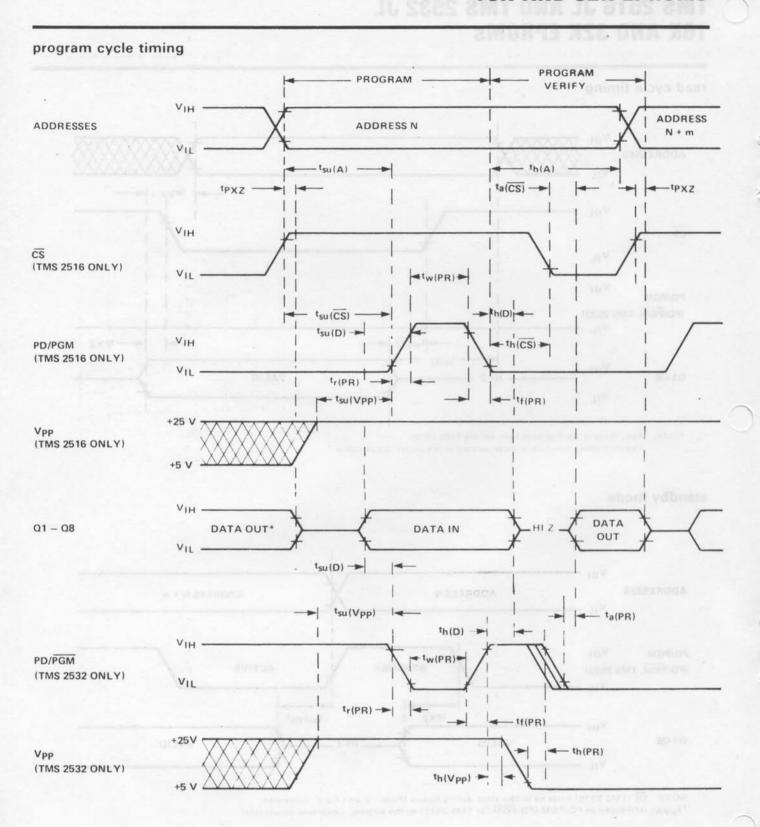

|              | 6.8   | Memory Timing CRU Address Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |

|              |       | Parallel I/O Port 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |

|              |       | 6.10.1 Input Channel Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |

|              |       | 6.10.2 Output Channel Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |

|              |       | 6.10.3 Polarity Inversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                 |

|              |       | 6.10.5 5MT Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                 |

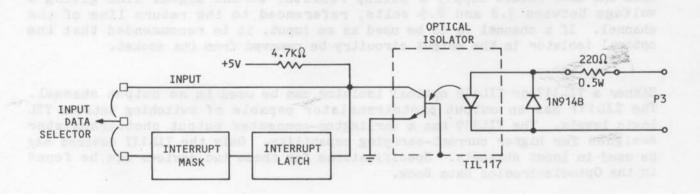

|              | 6.11  | Parallel Input Port 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                 |

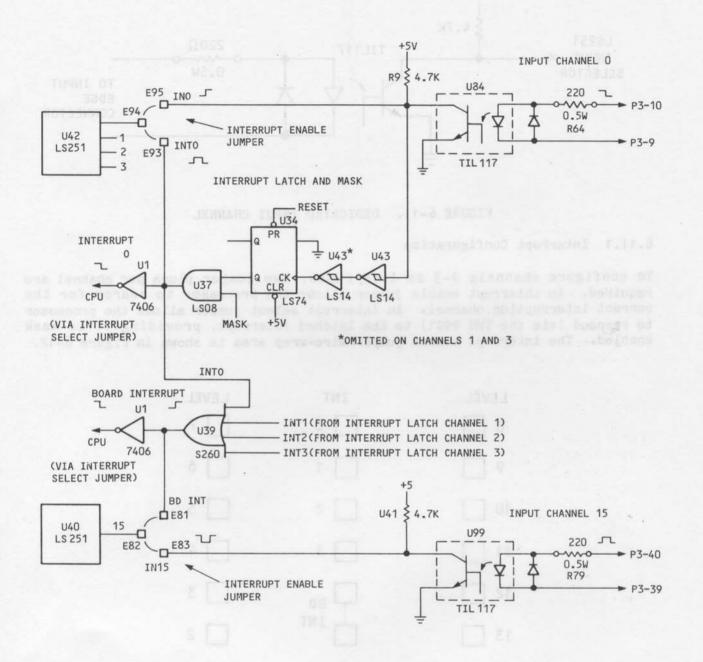

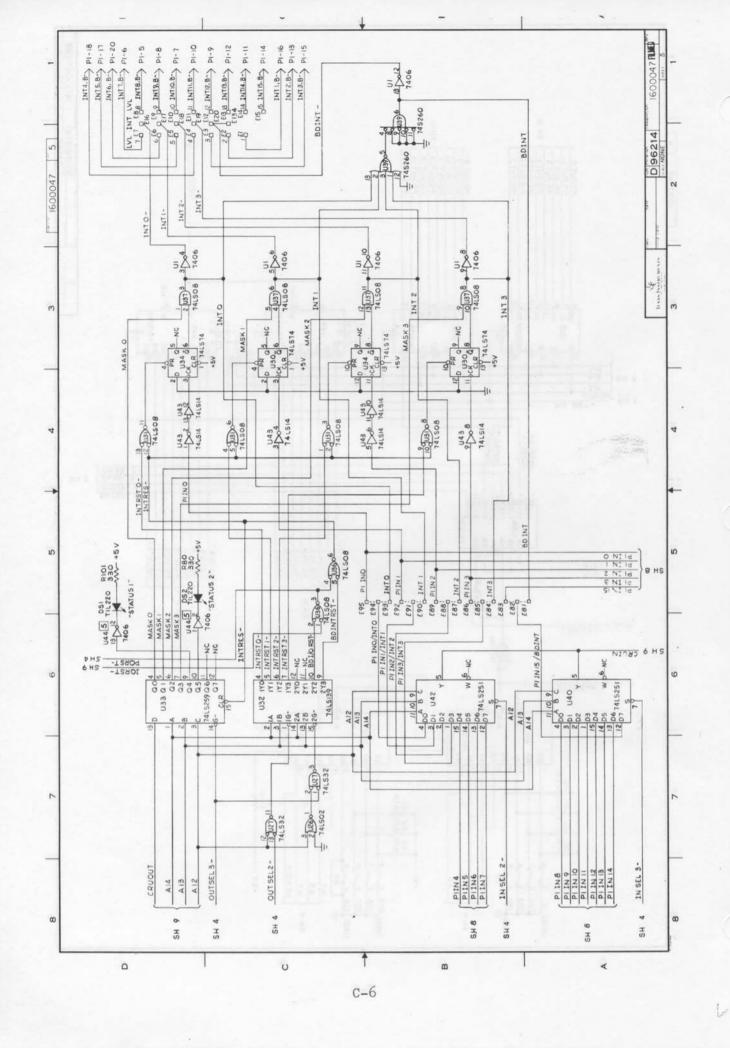

|              |       | 6.11.1 Interrupt Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |

|              |       | 6.11.2 Interrupt Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                 |

|              |       | 6.11.3 Interrupt Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                 |

|              | 6.12  | Board I/O Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                 |

|              |       | I/O Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                 |

|              |       | Status Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                 |

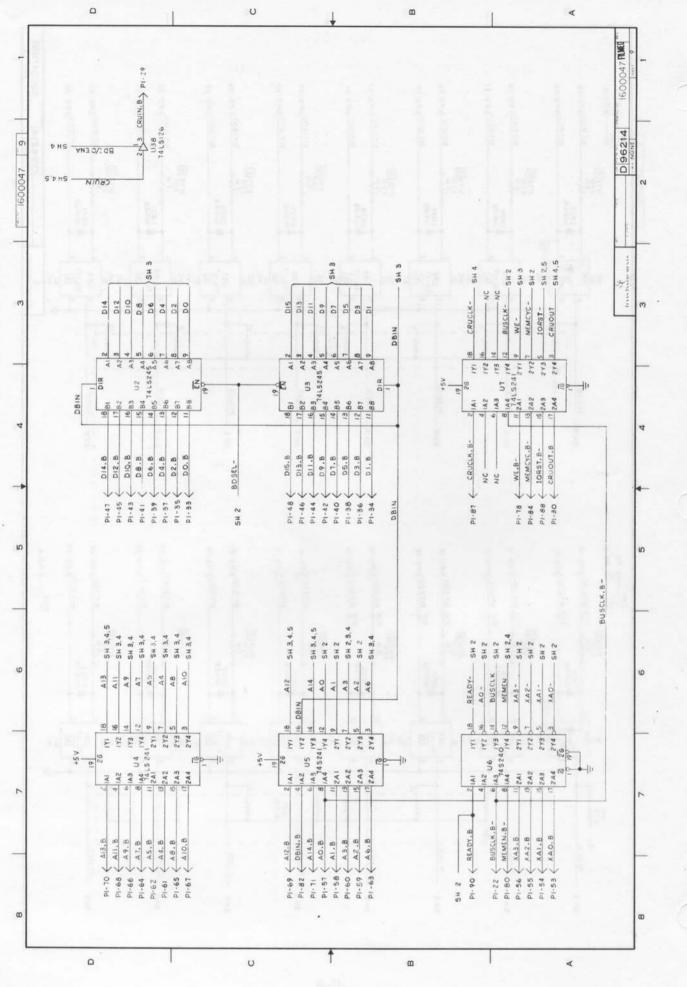

|              | 6.15  | Address And Control Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-22                                                                                            |

|              | 6.16  | Data Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-22                                                                                            |

# APPENDICES

| A<br>B | Input/Output Electrical Ratings Parts List          |

|--------|-----------------------------------------------------|

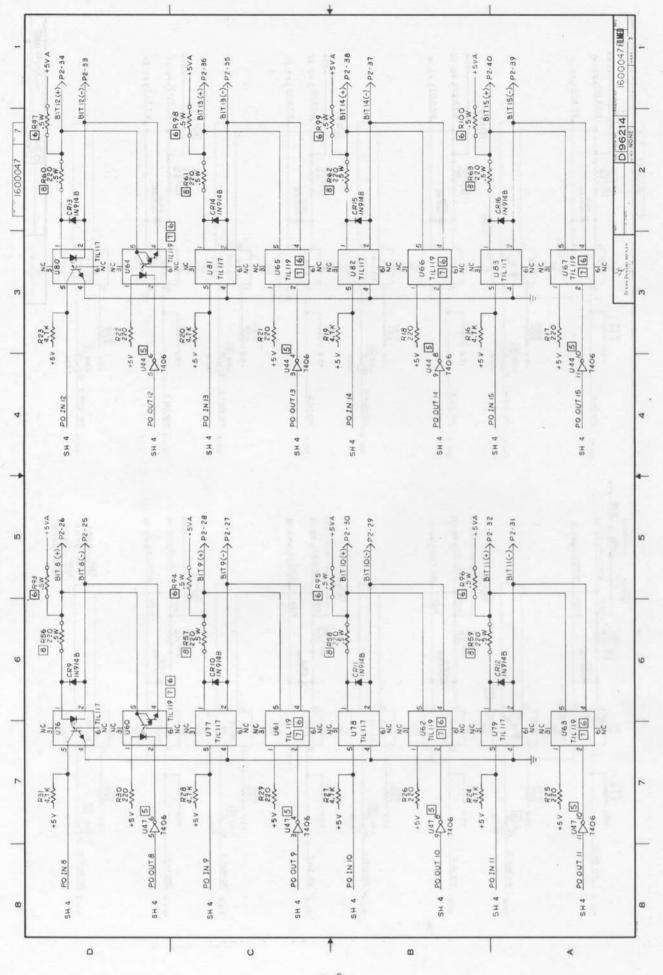

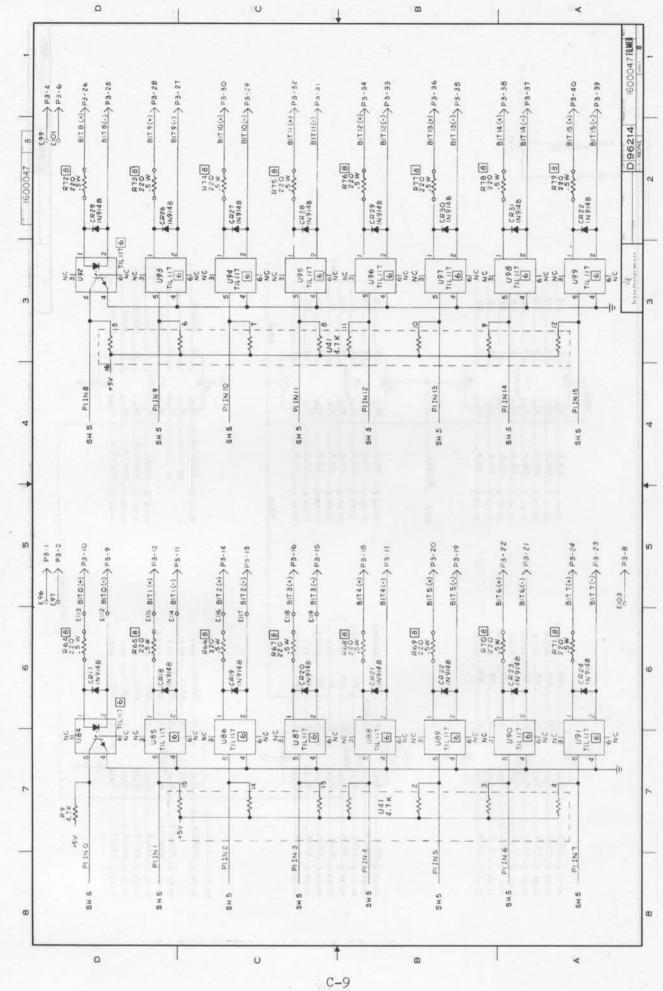

| C      | Schematics                                          |

| D      | Chassis Interface Connector (P1) Signal Assignments |

| E      | Edge Connector (P2, P3) Pin Assignments             |

| F      | 5MT Interface                                       |

| G      | TMS 4016 Data Sheet                                 |

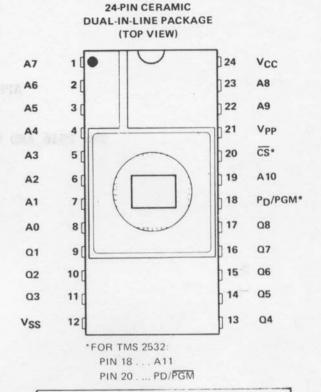

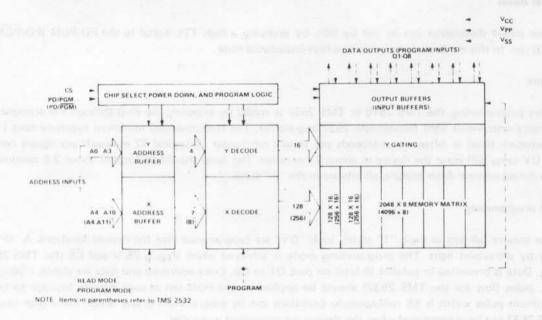

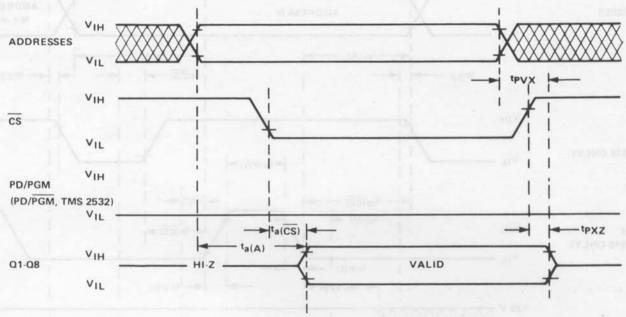

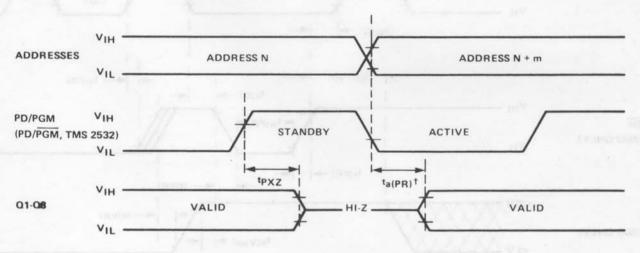

| Н      | TMS 2516 and TMS 2532 Data Sheets                   |

# LIST OF ILLUSTRATIONS

| FIGURE | A TITLE Intools suggestingel                            | PAGE |

|--------|---------------------------------------------------------|------|

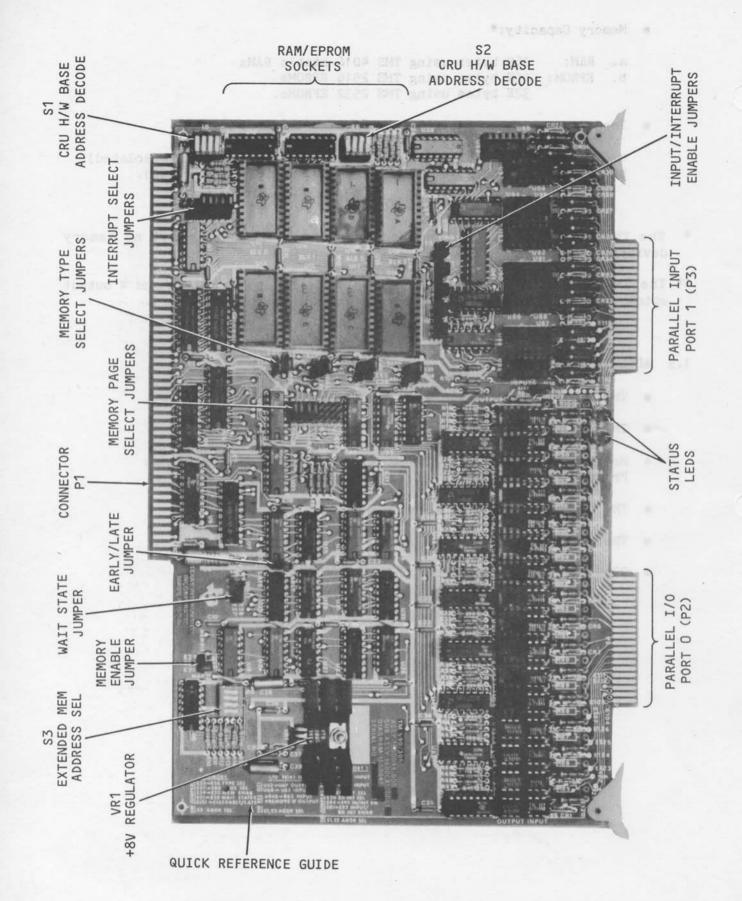

| 1-1    | TM 990/305 Principal Components                         | 1-4  |

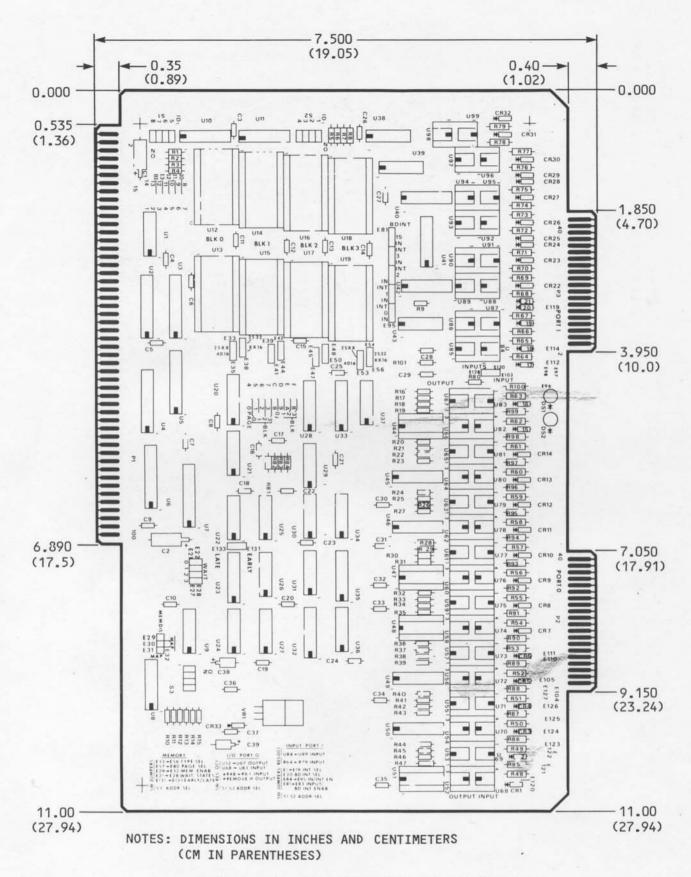

| 1-2    | TM 990/305 Module Dimensions                            | 1-5  |

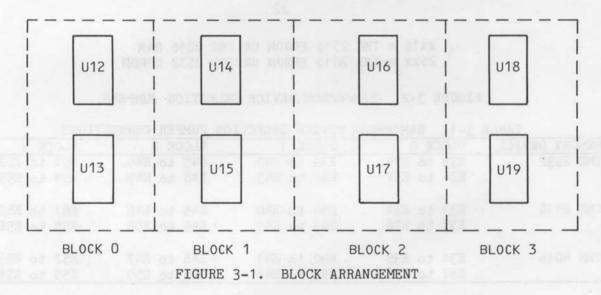

| 3-1    | Block Arrangement                                       | 3-1  |

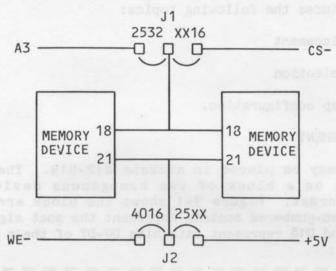

| 3-2    | RAM/EPROM Device Selection Jumpers                      | 3-2  |

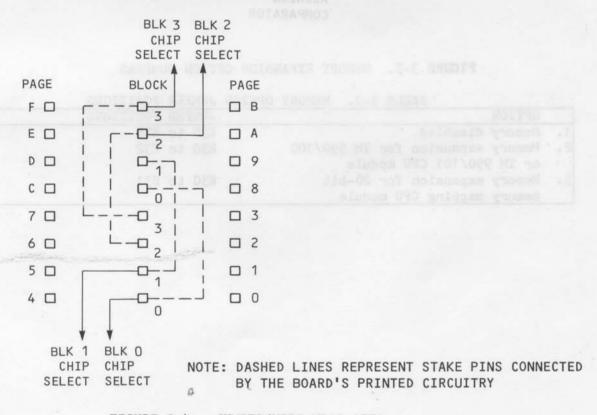

| 3-3    | Page Generation                                         | 3-3  |

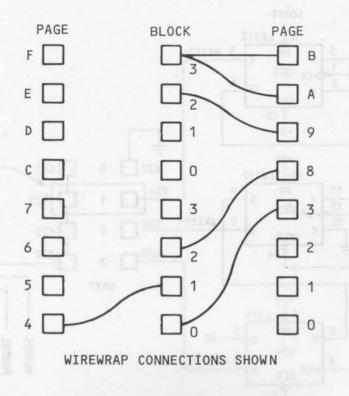

| 3-4    | Jumper/Wire-Wrap Area                                   | 3-3  |

| 3-5    | Memory Expansion Option Jumpers                         | 3-4  |

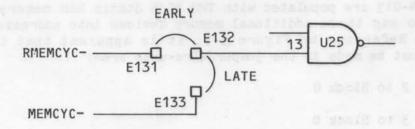

| 3-6    | Memory Cycle Jumper Connections                         | 3-5  |

| 3-7    | Memory Map Configurations                               |      |

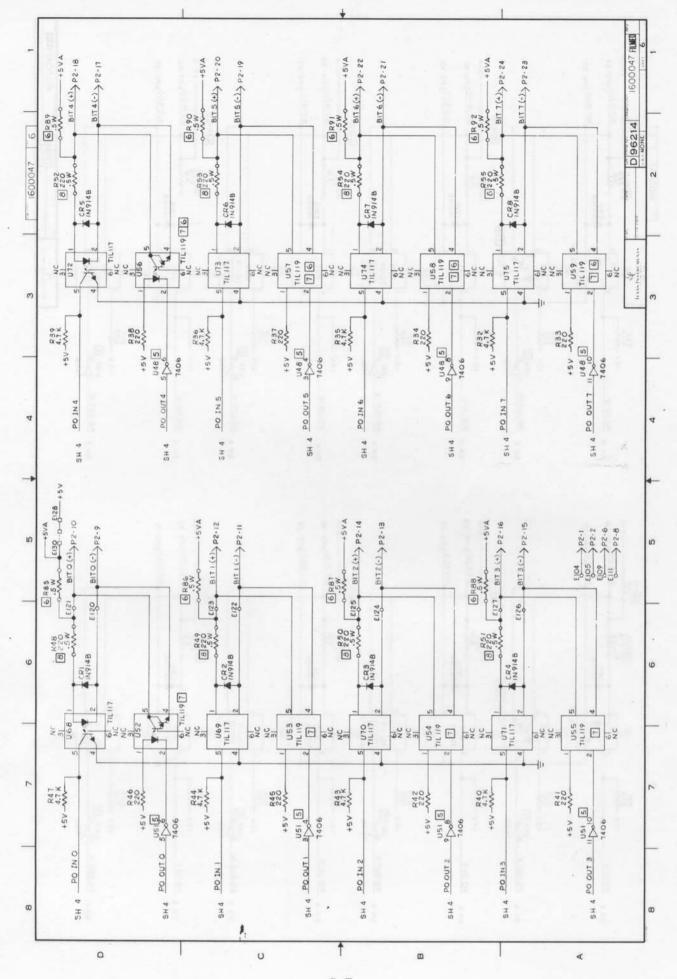

| 4-1    | Port 0 Circuitry (Channel 0)                            | 4-2  |

| 4-2    | Port 1 Circuitry (Channels 0-3)                         |      |

| 5-1    | I/O Ports at Edge Connectors P2 and P3                  | 5-1  |

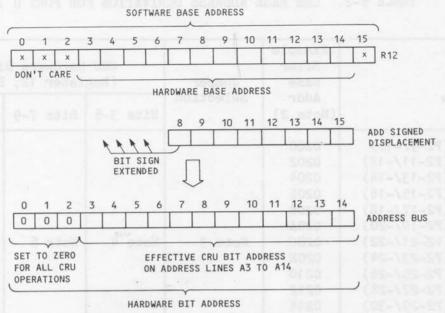

| 5-2    | CRU Addressing Nomenclature                             |      |

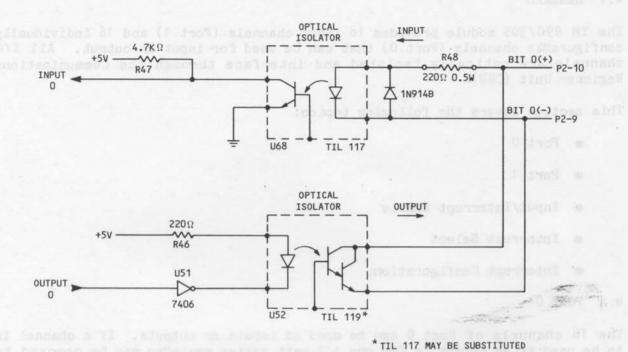

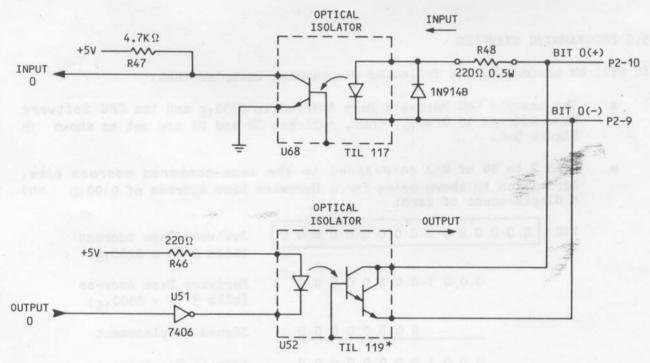

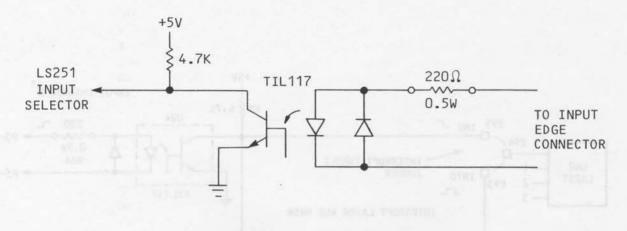

| 5-3    | Edge-Connector Opto-Coupler Interface                   | 5-7  |

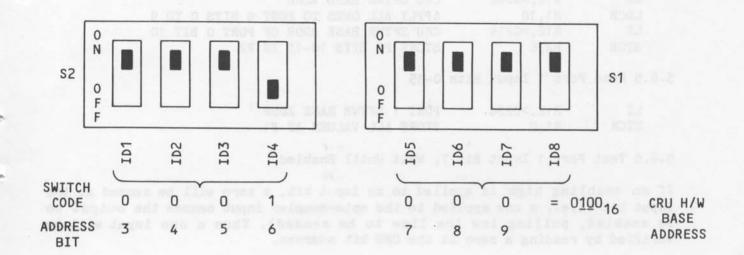

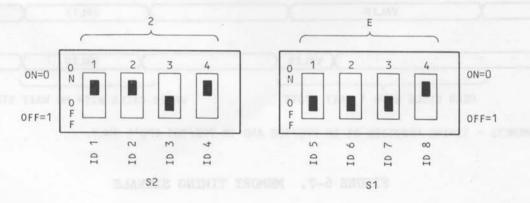

| 5-4    | Settings of Switches S2 and S1 for Programming Examples | 5-9  |

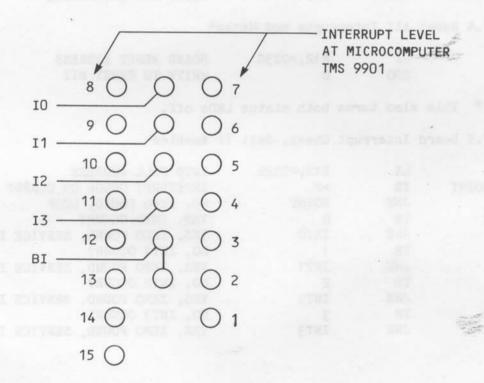

| 5-5    | Interrupt Jumper/Wire-Wrap Area                         | 5-11 |

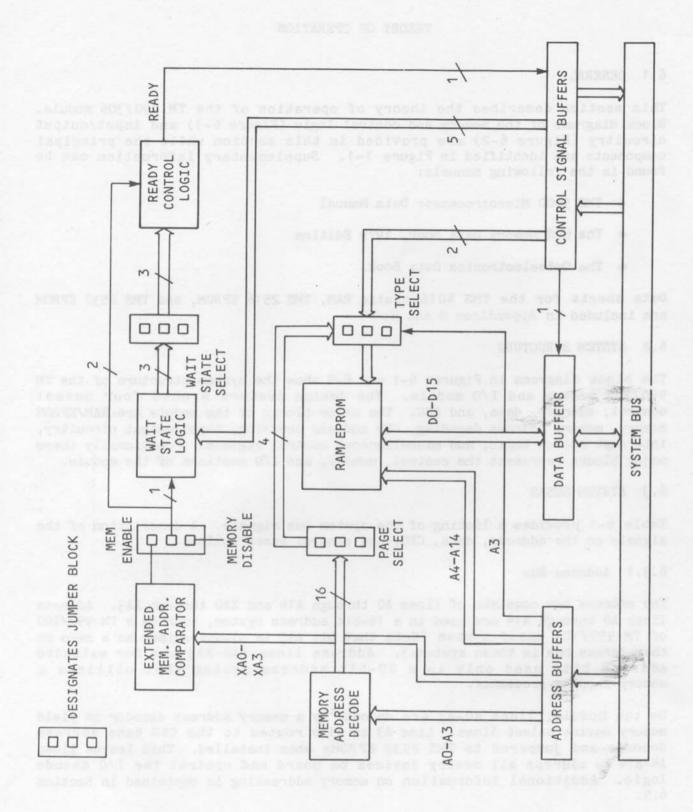

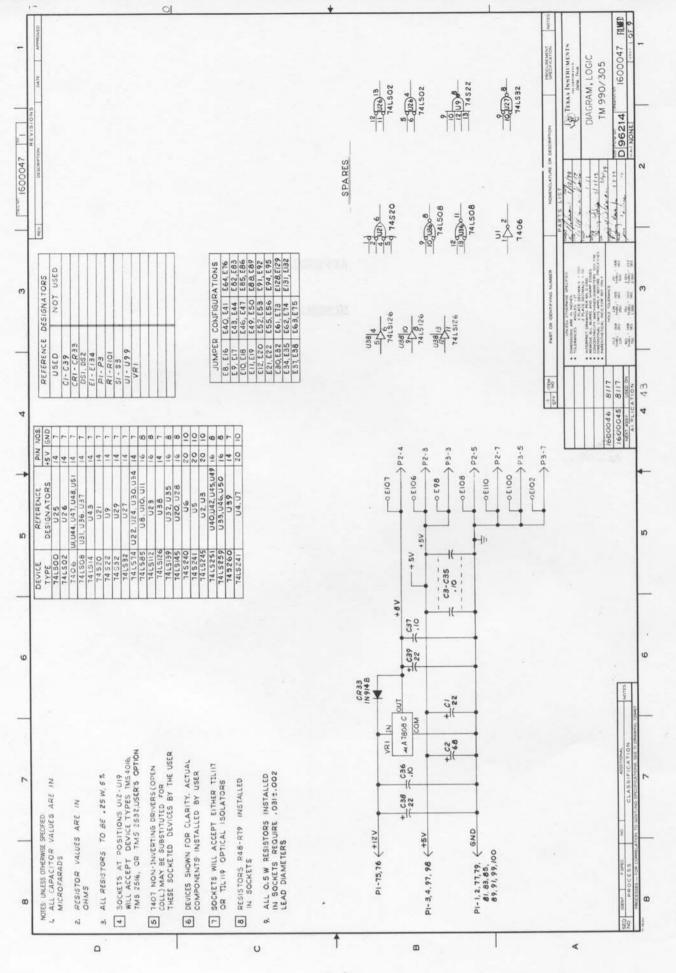

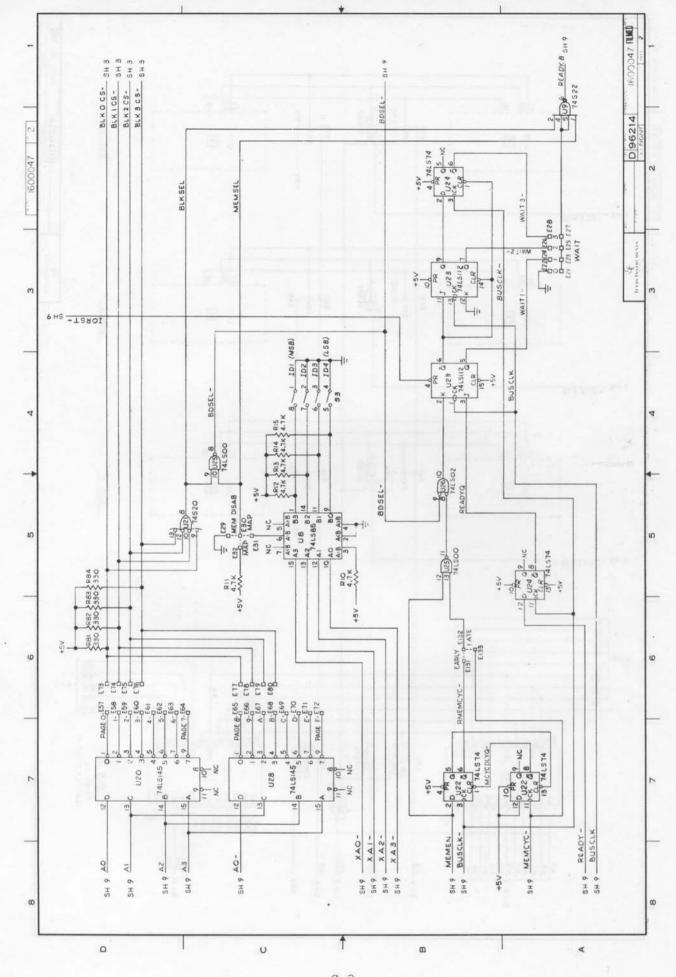

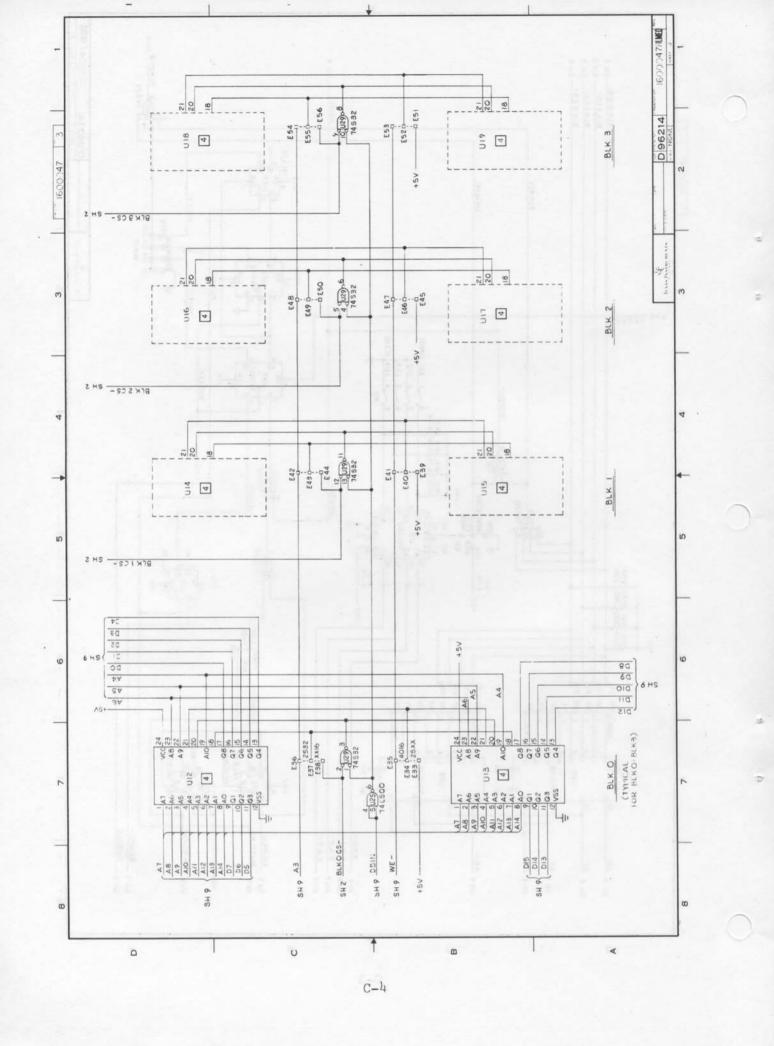

| 6-1    | Memory and Control Logic                                | 6-2  |

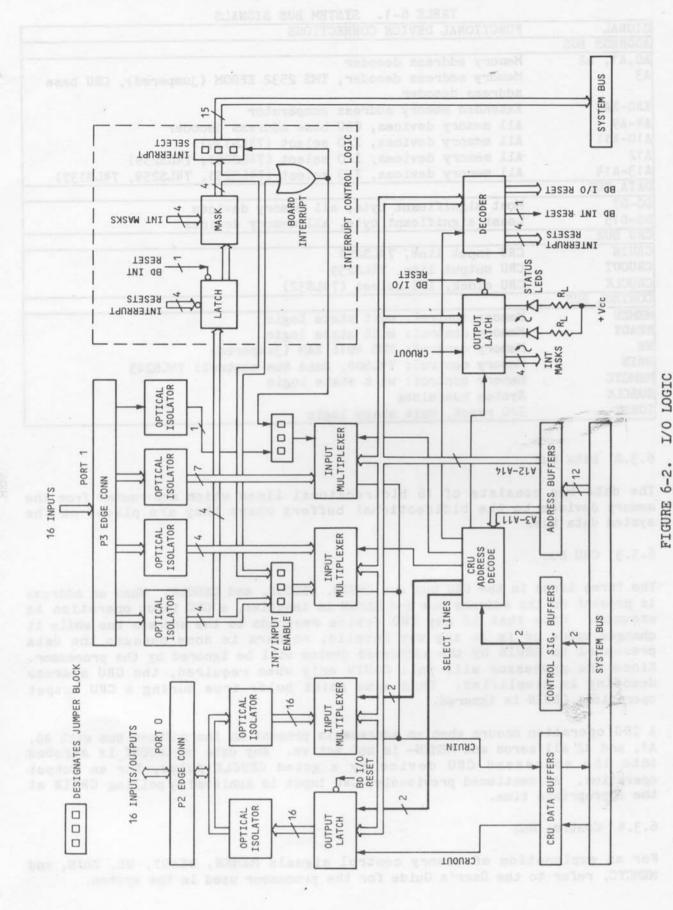

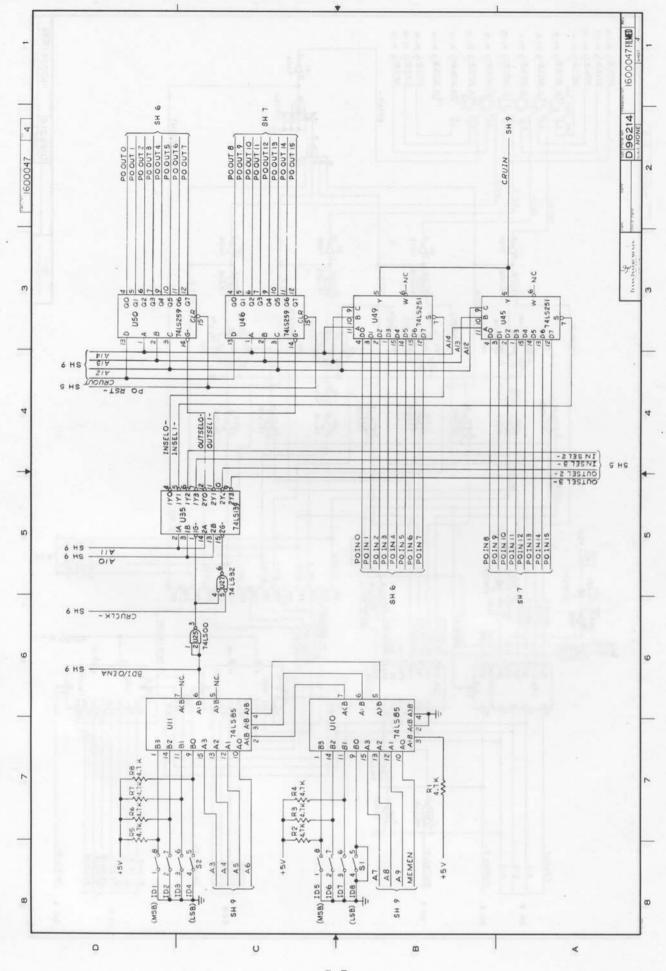

| 6-2    | I/O Logic                                               |      |

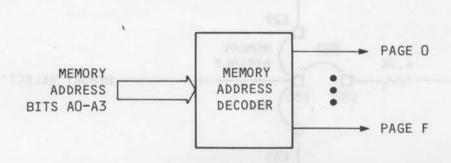

| 6-3    | Memory Address Decode                                   |      |

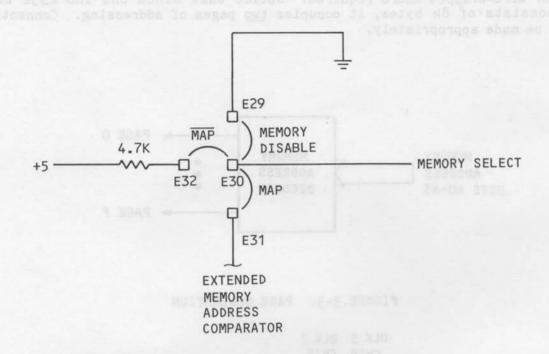

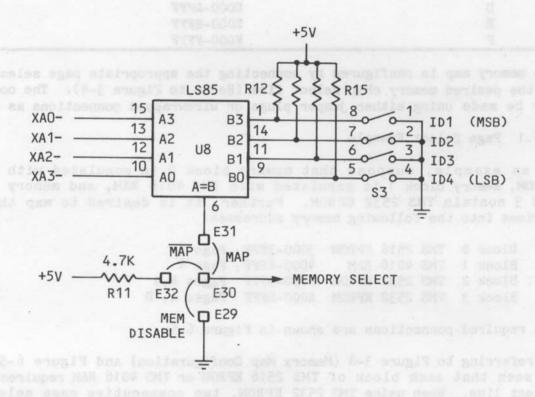

| 6-4    | Extended Address Decoding                               | 6-7  |

| 6-5    | Page Select Example                                     |      |

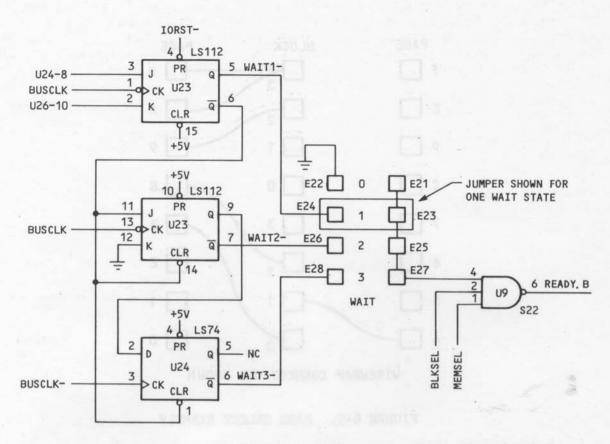

| 6-6    | Wait State Control and Ready Logic                      | 6-10 |

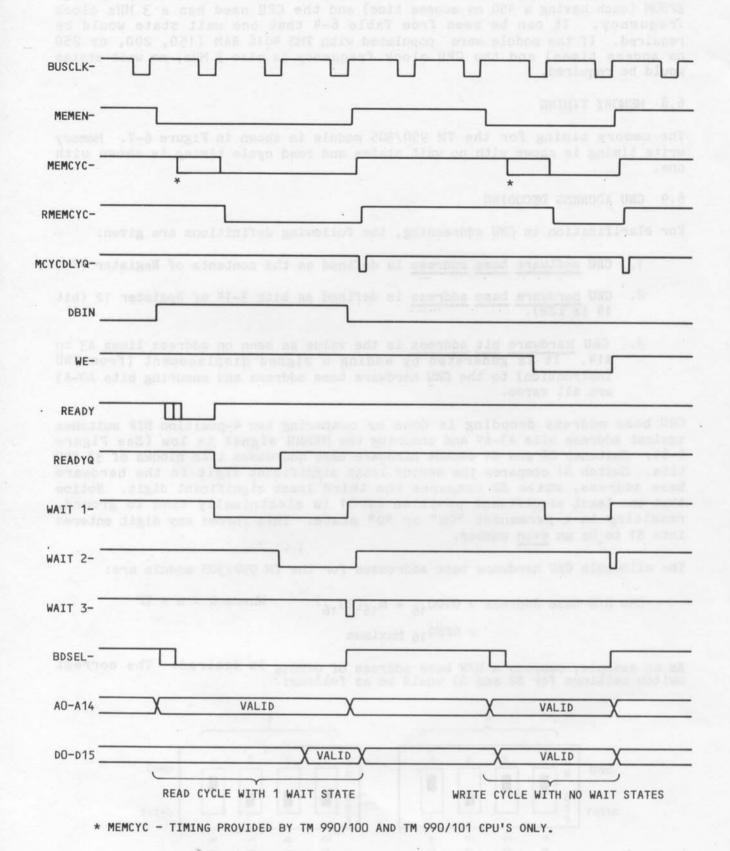

| 6-7    | Memory Timing Signals                                   | 6-12 |

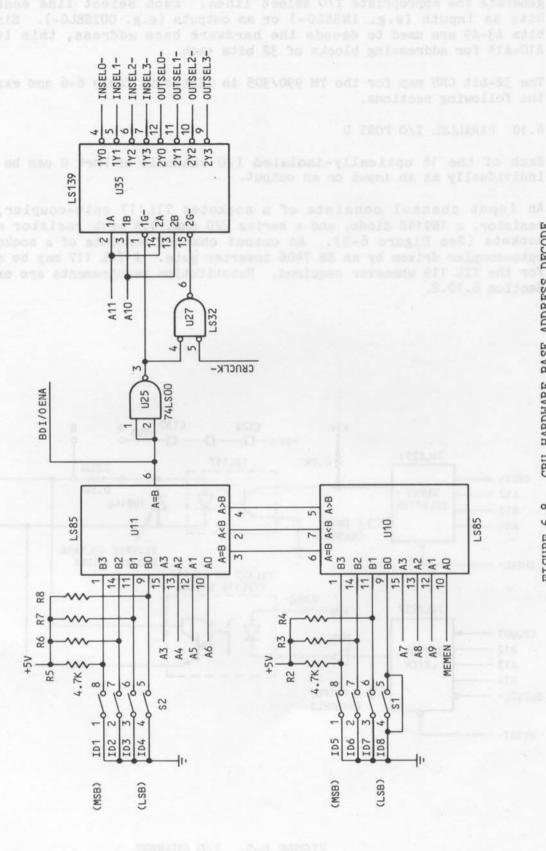

| 6-8    | CRU Hardware Base Address Decode                        |      |

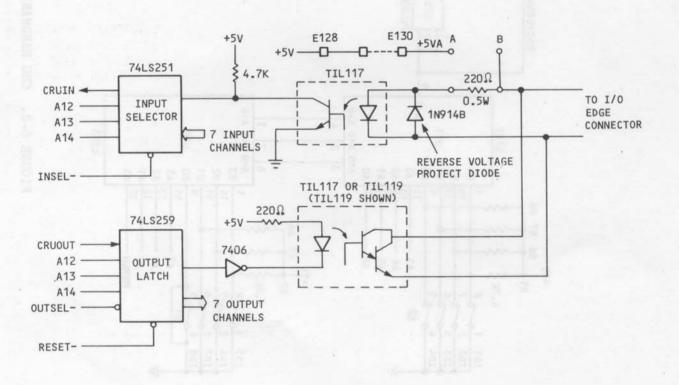

| 6-9    | I/O Channel                                             |      |

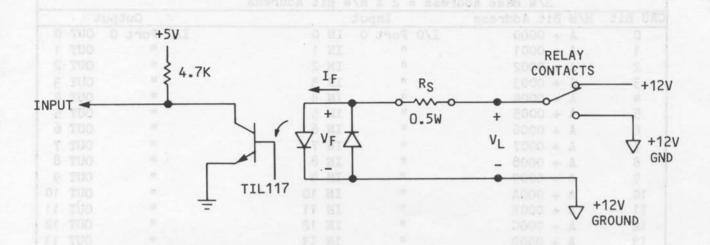

| 6-10   | Configurable Input Channels                             |      |

| 6-11   | Dedicated Input Channel                                 | 6-20 |

| 6-12   | Interrupt Select                                        |      |

|        |                                                         |      |

# LIST OF TABLES

| TABLE                                  | TITLE                                                                                                                                                                    | PAGE                         |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 2-1<br>2-2                             | Module Jumper Positions as Shipped                                                                                                                                       |                              |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5        | RAM/EPROM Device Selection Jumper Connections  Memory Option Jumper Positions  Wait States  Jumper Positions for Different Memory Wait States  Memory Address Boundaries | 3-4<br>3-5<br>3-5            |

| 4-1<br>4-2                             | Input/Interrupt Enable Jumpers                                                                                                                                           |                              |

| 5-1<br>5-2<br>5-3<br>5-4               | Edge Connector (P2 and P3) Pin Assignments                                                                                                                               | 5 <b>-</b> 4<br>5 <b>-</b> 5 |

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6 | System Bus Signals  Quick Reference Guide  Memory Address Boundaries  Wait States  Memory Access Times  CRU Map                                                          | 6-5<br>6-8<br>6-10<br>6-10   |

# SECTION 1

#### INTRODUCTION

# 1.1 GENERAL

The TM 990/305 is a combination memory and input/output expansion module. This module can comprehend a 16-bit address, as used in a TM 990/10X system, or a 20-bit address, as used in a system utilizing a memory-mapping CPU. The TM 990/305 has a memory capacity of 32K bytes. Memory configuration is significantly enhanced by allowing the use of either static RAM or EPROM in each of the memory sockets. This module has 16 parallel input channels (Port 1) and 16 parallel input/output channels (Port 0) that can be configured individually as either inputs or outputs. All I/O channels are optically isolated and interface through the Communications Register Unit (CRU).

Input/output flexibility is designed into the TM 990/305 to allow the user to configure the I/O channels to meet his requirements. Input channels may be configured for input voltages up to 30 V, while output channels may be configured for TTL compatibility or as current drivers. Output channel polarity can be selected by the user as either inverting or non-inverting. For details, refer to Sections 4 and 6.

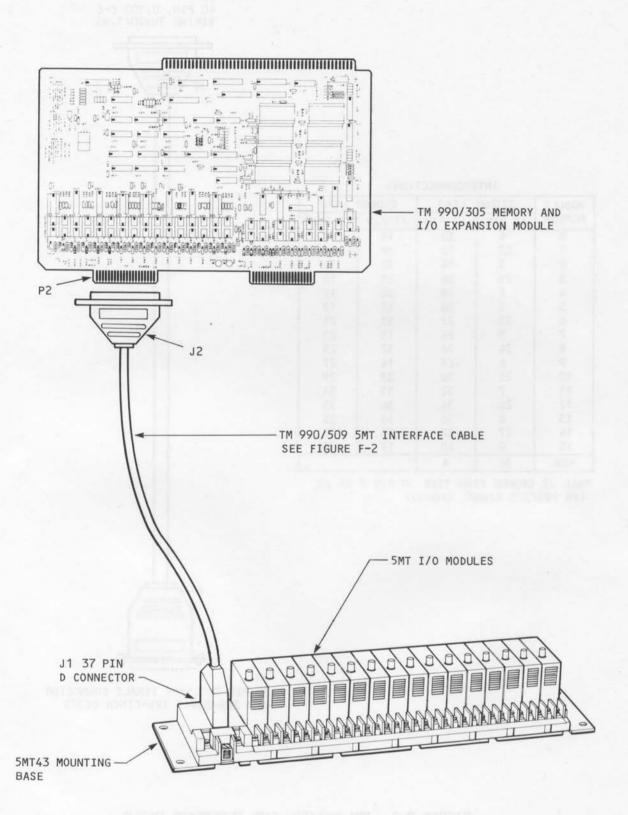

5MT industrial I/O interface capability is provided on the TM 990/305 module. An on-board voltage regulator supplies the required +8 V  $V_{\rm CC}$  while the required pullup resistors for the I/O channels can be installed in sockets provided on the module. A TM 990/509 cable is then required to connect the TM 990/305 to a 5MT I/O system. Selection and placement of the proper resistors are explained in Section 6.10.5 and the appropriate interconnections are shown in Appendix F.

The TM 990/305 module offers the following features:

- Compatible with the TM 990 microcomputer system bus

- Designed to fit either the TM 990/510 or TM 990/520 card cage

- Designed to interface with the TM 990/100 or /101 CPU modules

- 16 or 20-bit address handling capability

- Memory capacity of 16K bytes (using TMS 4016 RAMs or TMS 2516 EPROMs)

- Memory capacity of 32K bytes (using TMS 2532 EPROMs)

- Jumper/wirewrap decoder to permit easy reassignment of memory map configuration

- 16 optically-isolated parallel input channels

- 16 optically-isolated parallel input/output channels, user-configurable

- Capability of reconfiguring input channels for voltages up to 30 V

- Output channels may be configured for TTL compatibility or as current drivers

- Switch selection to permit easy reselection of CRU base address

- 4 edge-triggered, latched interrupts user-configurable to interrupt levels 1-15

- 5MT interface capability using TM 990/509 cable assembly.

# 1.2 MANUAL ORGANIZATION

This manual is organized as follows:

- Section 1 covers module specifications and characteristics.

- Section 2 explains how to install and check out the TM 990/305 module.

- Section 3 covers memory placement and selection.

- Section 4 covers input/output port configurations.

- Section 5 presents the fundamental concepts involved in I/O and interrupt programming.

- Section 6 covers theory of operation, explaining the hardware design, configuration and circuitry.

# 1.3 MODULE CHARACTERISTICS

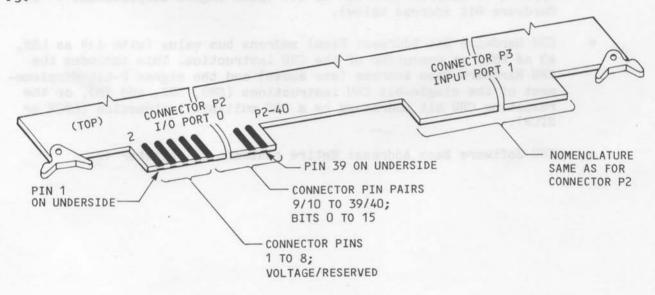

Figure 1-1 shows the principal components and interfaces of the TM 990/305 module. The system bus connector is P1, which is a 100-pin (50 each side) PC board edge connector spaced on 0.125 inch centers. Connector P2 interfaces with Port 0 and P3 interfaces with Port 1. A ribbon or twisted-pair cable with a 40-pin, 0.1-inch center spacing PCB edge connector will be required for each port used.

Figure 1-2 shows the PC module silkscreen markings which detail the various components on the module; also included are the module dimensions and tolerances.

# 1.4 GENERAL SPECIFICATIONS

• Power Requirements:  $+5 \text{ V} \pm 3\%$ , 1.5 A.

To interface with a 5MT industrial control system, a +12 V  $\pm$ 3%, 0.75 A power supply is required.

- Operating Temperature: 0°C to 70°C.

- Module Dimensions: See Figure 1-2.

- Memory Capacity:\*

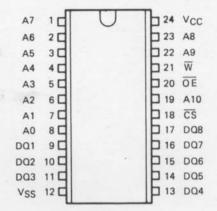

- a. RAM: 16K bytes using TMS 4016 static RAMs

- b. EPROM: 16K bytes using TMS 2516 EPROMs 32K bytes using TMS 2532 EPROMs.

- Input/Output Capability: \*\*

- a. Port 0: 16 parallel input/output channels (optically-isolated)

- b. Port 1: 16 parallel input channels (optically-isolated).

#### NOTES

- \* The TM 990/305 module is shipped with memory sockets only; no memory devices are shipped.

- \*\* The TM 990/305 module is shipped with 16 input opto-couplers and 4 output opto-couplers in Port 0. No opto-couplers are shipped in Port 1.

#### 1.5 APPLICABLE DOCUMENTS

- TMS 9900 Microprocessor Data Manual

- TM 990/100 or /101 Microcomputer User's Manual

- Model 990 Computer TMS 9900 Microprocessor Assembly Language Programmer's Guide

- The MOS Memory Data Book, 1979 Edition

- The Optoelectronics Data Book

- 9900 Family Systems Design and Data Book

FIGURE 1-1. TM 990/305 PRINCIPAL COMPONENTS

FIGURE 1-2. TM 990/305 MODULE DIMENSIONS

#### SECTION 2

# INSTALLATION AND CHECKOUT OF TM 990/305 MODULE

#### 2.1 GENERAL

The following topics are described in this section:

- Equipment required for TM 990/305 module operation

- Unpacking and inspection

- Jumper configuration

- Switch configuration

- Power supply connections

- · Operational checkout.

It is presumed that the user is familiar with the hardware and programming of the host microcomputer. This data is available in the TM 990/100 or /101 Microcomputer User's Guide.

#### 2.2 REQUIRED EQUIPMENT

The basic equipment required to use a TM 990/305 module in a microcomputer system is described in the following paragraphs.

# 2.2.1 Host Microcomputer

The TM 990/305 module can be used with either the TM 990/100 or TM 990/101 CPU modules or a memory-mapping CPU module.

### 2.2.2 Terminal Device

Any RS-232-C device operable at a baud rate acceptable to the software being used or an ASR33 Teletype modified for 20 mA current loop operation interfaced to the CPU module can be used. TIBUG software supplies 110, 300, 1200 and 2400 baud, and certain versions provide additional rates such as 9600 or 19200 baud.

# 2.2.3 Power Supply

A dc power supply capable of supplying +5 Vdc @ 1.5 A is required. When interfacing with a 5MT system, a +12 Vdc @ 0.75 A power supply is required.

# 2.2.4 Card Cage/System Bus Connector

Use of either the TM 990/510 or TM 990/520 card cage greatly facilitates operation and setup. The TM 990/305 communicates with the CPU module via the 100-pin bus interface socket of the card cage. Alternately, one of the following 100-pin, 0.125 inch (center-to-center) PCB edge connectors may be used to interface with connector P1. Appropriate wire-wrap connector types

are listed below:

- TI H321150

- Amphenol 225-804-50

- Viking 3VH50/9CND5

# 2.2.5 Parallel I/O Connector

I/O interface is accomplished through connectors P2 and P3. P2 interfaces with Port O and P3 interfaces with Port 1. A ribbon or twisted-pair cable with a 40-pin, 0.100 inch center spacing PCB edge connector will be required for each port used. Appropriate connector types are given below:

- TI H312120 (Solder Tail)

- Viking 3VH20/1JN5 (Pierced Tail)

- 3M 3464-0001 (Ribbon Cable)

# 2.3 UNPACKING AND INSPECTION

Remove the TM 990/305 module from its carton and remove the protective wrapping. Check the module for shipping damage. If any damage is found, notify your TI distributor.

# 2.4 JUMPER CONFIGURATION AS SHIPPED

Check the module and verify that the jumper configuration is as described in Table 2-1.

TABLE 2-1. MODULE JUMPER POSITIONS AS SHIPPED

| FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | STAKE PINS USED   | PROPER CONNECTION & DESCRIPTION |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------|

| CPU Interrupt Levels 1-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | E1 through E15    | E8 to E16 (Level 8 to Source 0) |

| Interrupt Sources 0-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | E16 through E19   | E9 to E17 (Level 9 to Source 1) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | E10 to E18 (Level 10 to Srce 2) |

| The state of the s |                   | E11 to E19 (Level 11 to Srce 3) |

| Board interrupt Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | E20, E134         | E12 to E20 (Level 12 to Bd Int) |

| Memory Wait States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | E21 through E28   | E21 to E22 No Wait States       |

| Memory Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | E29 through E32   | E30 to E32 Enable memory for    |

| Loop operation inhestrated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | /100 or /101 CPU                |

| Memory Type Select BLK0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | E33 through E38   | E34 to E35, E37 to E38 TMS 4016 |

| BLK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | E39 through E44   | E40 to E41, E43 to E44 TMS 4016 |

| BLK2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | E45 through E50   | E46 to E47, E49 to E50 TMS 4016 |

| BLK3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | E51 through E56   | E52 to E53, E55 to E56 TMS 4016 |

| Memory Page Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | E57 through E80   | E61 to E73, (Page 4 to Block 0) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | E62 to E74, (Page 5 to Block 1) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | E63 to E75, (Page 6 to Block 2) |

| nedW . hertigees at A B.F.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | E64 to E76, (Page 7 to Block 3) |

| Input/Board Int Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | E81 through E83   | E82 to E83 Input Enabled        |

| Input/Interrupt O Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | E84 through E86   | E85 to E86 Input Enabled        |